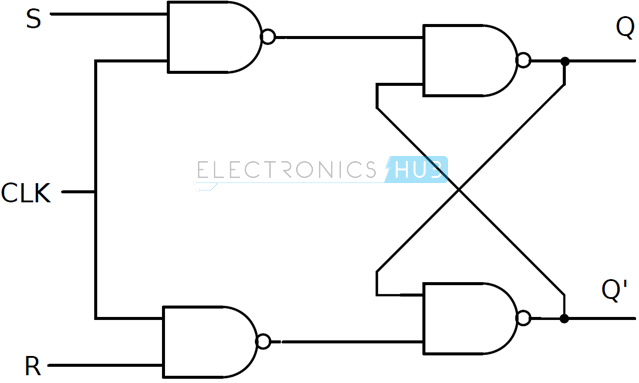

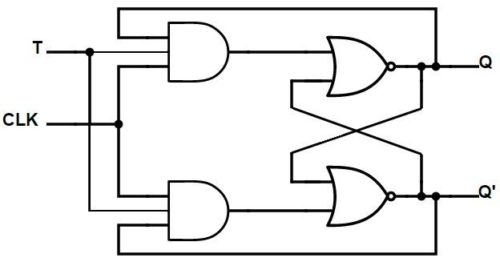

These are used as one-bit storage elements, clock dividers and also we can make counters, shift registers, and storing registers by connecting the flip flops in particular sequences. Find, read and cite all the research you. #Edge triggered flip flop by using nor gates pdfThe timing required will depend on the speed of your circuit. Flip flops are one of the most fundamental electronic components. PDF In this paper, a single edge-triggered, static D flip-flop design suitable, for low power and low area requirements is proposed. However, you need to make sure that the output pulse is wide enough that the J-K circuit stabilizes after a transition in state happens. The FF includes two states shown in the following figure. The diagram and truth table is shown below. S-R Flip Flop using NOR Gate The design of such a flip flop includes two inputs, called the SET S and RESET R. These flip flops are also called S-R Latch. This kind of flip flop is stated to as an SR flip flop or SR latch. The SET-RESET flip flop is designed with the help of two NOR gates and also two NAND gates. Each flip flop consists of two inputs and two outputs, namely set and reset, Q and Q’. To your second question: yes, the NOT AND circuit you show implements the desired pulse-creation circuit. The designing of the flip flop circuit can be done by using logic gates such as two NAND and NOR gates. A solution to this is to keep the control input high only on the edge of an input: thus the edge/pulse detection circuit. However, since the J-K operation function isn't simple like the D case, some other method of making the flip-flop edge sensitive is needed. Public Domain work from the Wikimedia Commons A solution to this with D latches is to put two latches in series with \$180^\$ difference in clock phase in the Master–slave edge-triggered D flip-flop configuration: Like the NOR Gate S-R flip flop, this one also has four states. That is, state can "flow" from J and K to Q if the control signal is always logic high. S-R Flip Flop using NAND Gate The circuit of the S-R flip flop using NAND Gate and its truth table is shown below. It has two inputs, one is called SET which will set the device and another is known as RESET which will reset. The four-gate AND NOR circuit you see is actually a latch with respect to the control input. The RS Flip Flop is considered as one of the most basic sequential logic circuits.

#Edge triggered flip flop by using nor gates generatorYes, the edge detector/pulse generator is needed to operate the circuit as a J-K flip-flop.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed